LM3643, LM3643A

SNVS967A-AUGUST 2014-REVISED NOVEMBER 2014

Support &

Community

20

# LM3643 Synchronous Boost Dual LED Flash Driver with 1.5-A High-Side Current Sources

Technical

Documents

Sample &

Buy

#### 1 Features

- 1.5 A Total Allowed LED Current During Operation (I<sub>LED1</sub> + I<sub>LED2</sub> = 1.5 A)

- Dual Independent LED Current Source

Programmability

- Accurate and Programmable LED Current Range from 1.4 mA to 1.5 A

- Optimized Flash LED Current During Low Battery Conditions (IVFM)

- > 85% Efficiency in Torch Mode (@ 100 mA) and Flash Mode (@1 A to 1.5 A)

- Grounded Cathode LED Operation for Improved Thermal Management

- Small Solution Size: < 16 mm<sup>2</sup>

- Hardware Strobe Enable (STROBE)

- Synchronization Input for RF Power Amplifier Pulse Events (TX)

- Hardware Torch Enable (TORCH/TEMP)

- Remote NTC Monitoring (TORCH/TEMP)

- 400-kHz I<sup>2</sup>C-Compatible Interface

- LM3643 (l<sup>2</sup>C Address = 0x63)

- LM3643A ( $I^2C$  Address = 0x67)

#### 2 Applications

Camera Phone White LED Flash

#### 3 Description

Tools &

Software

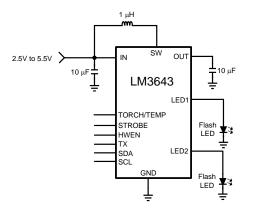

The LM3643 is a dual LED flash driver that provides a high level of adjustability within a small solution size. The LM3643 utilizes a 2-MHz or 4-MHz fixedfrequency synchronous boost converter to provide power to the dual 1.5-A constant current LED sources. The total LED current the LM3643 boost can deliver is 1.5 A ( $I_{LED1}$  +  $I_{LED2}$ ). The dual 128 level current sources provide the flexibility to adjust the current ratios between LED1 and LED2 with each driver capable of delivering a maximum of 1.5 A (ex:  $I_{LED1} = 1.5 \text{ A and } I_{LED2} = 0 \text{FF}, I_{LED1} = 0 \text{FF} \text{ and } I_{LED2} =$ 1.5 A, or a current configuration with a current less than 1.5 A ,  $I_{\text{LED1}}$  = 950 mA and  $I_{\text{LED2}}$  = 250 mA). An adaptive regulation method ensures the current sources remain in regulation and maximizes efficiency.

Features of the LM3643 are controlled via an  $I^2C$ compatible interface. These features include: hardware flash and hardware torch pins (STROBE and TORCH/TEMP), a TX interrupt, and an NTC thermistor monitor. The device offers independently programmable currents in each output leg to drive the LEDs in a Flash or Movie Mode (Torch) condition.

The 2-MHz or 4-MHz switching frequency options, overvoltage protection (OVP), and adjustable current limit allow for the use of tiny, low-profile inductors and (10- $\mu$ F) ceramic capacitors. The device operates over a -40°C to 85°C ambient temperature range.

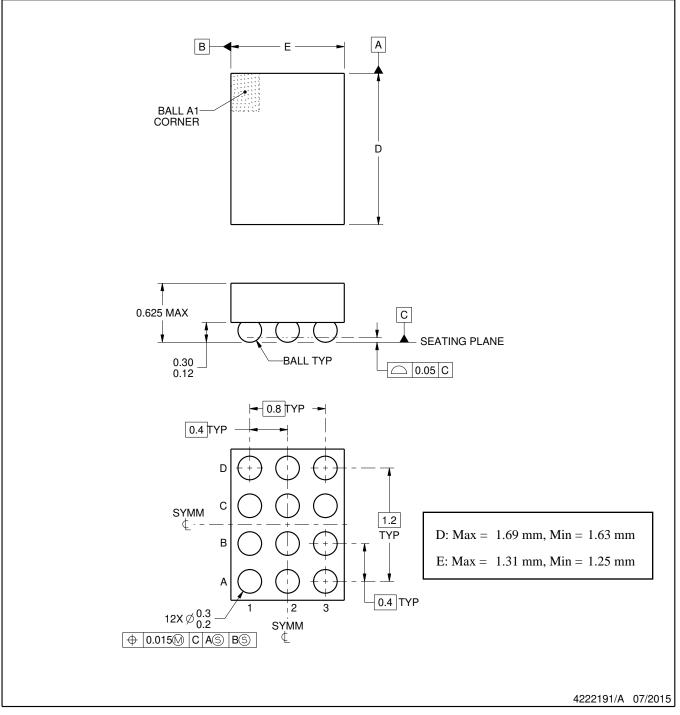

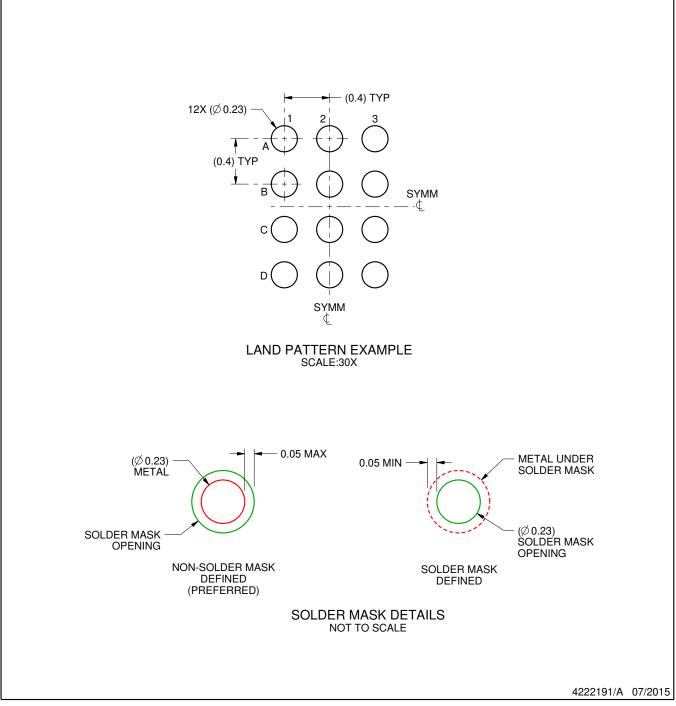

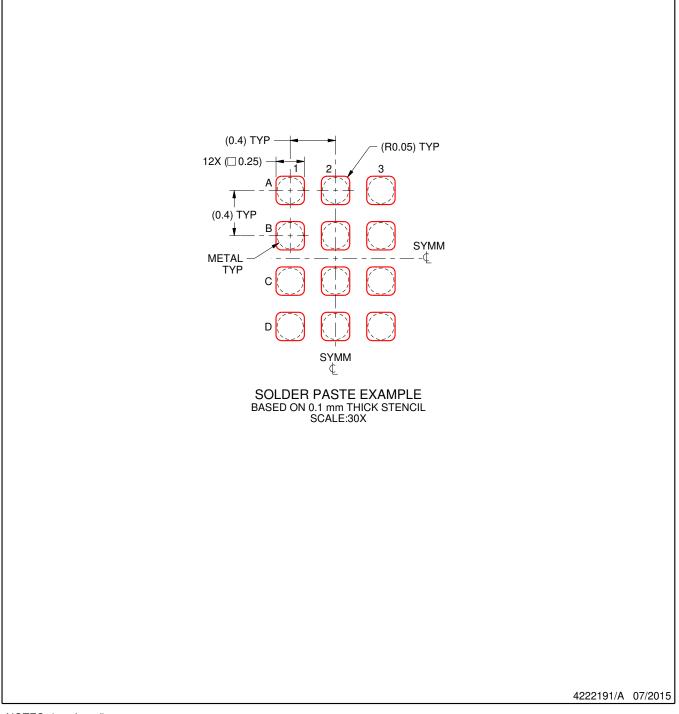

Device Information<sup>(1)</sup>

| Device information |            |                   |  |  |  |

|--------------------|------------|-------------------|--|--|--|

| PART NUMBER        | PACKAGE    | BODY SIZE (MAX)   |  |  |  |

| LM3643             | DSBGA (12) | 1.69 mm x 1.31 mm |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

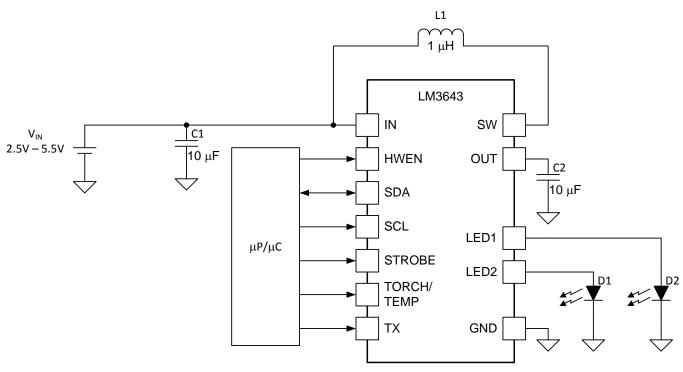

### 4 Simplified Schematic

### **Table of Contents**

| 1 | Fea  | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Sim  | plified Schematic1                 |

| 5 | Rev  | ision History 2                    |

| 6 | Dev  | ice Comparison Table 2             |

| 7 | Pin  | Configuration and Functions 3      |

| 8 | Spe  | cifications 4                      |

|   | 8.1  | Absolute Maximum Ratings 4         |

|   | 8.2  | Handling Ratings 4                 |

|   | 8.3  | Recommended Operating Conditions 4 |

|   | 8.4  | Thermal Information 4              |

|   | 8.5  | Electrical Characteristics5        |

|   | 8.6  | Timing Requirements 5              |

|   | 8.7  | Switching Characteristics 5        |

|   | 8.8  | Typical Characteristics 6          |

| 9 | Deta | ailed Description 10               |

|   | 9.1  | Overview 10                        |

|   | 9.2  | Functional Block Diagram 11        |

# **5** Revision History

| Cł | hanges from Original (August 2014) to Revision A | Page |

|----|--------------------------------------------------|------|

| •  | Added Information about LM3643A                  | 1    |

| •  | Changed 0x00 to 0x02 - typo                      | 19   |

| •  | Changed '011' to '000' - typo                    | 22   |

### 6 Device Comparison Table

| ORDERING PART NUMBER | I <sup>2</sup> C ADDRESS |

|----------------------|--------------------------|

| LM3643YFFR           | 0x63                     |

| LM3643AYFFR          | 0x67                     |

#### www.ti.com Feature Description ..... 12 9.3 Device Functioning Modes...... 13 9.4 Programming...... 17 9.5 9.6 Register Descriptions ...... 19 10 Applications and Implementation...... 23 10.2 Typical Application ..... 23 11 Power Supply Recommendations ...... 29 12.1 Layout Guidelines ...... 29 12.2 Layout Example ...... 30 13 Device and Documentation Support ...... 31 13.1 13.2 13.3 Trademarks ...... 31

#### Mechanical, Packaging, and Orderable 14

Copyright © 2014, Texas Instruments Incorporated

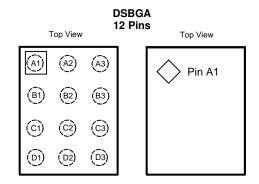

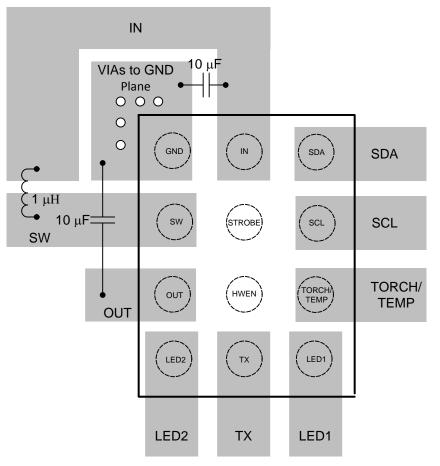

# 7 Pin Configuration and Functions

#### **Pin Functions**

| I      | PIN        | DESCRIPTION                                                                                                                                       |

|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME       | DESCRIPTION                                                                                                                                       |

| A1     | GND        | Ground                                                                                                                                            |

| A2     | IN         | Input voltage connection. Connect IN to the input supply and bypass to GND with a $10\mathchar`\mu F$ or larger ceramic capacitor.                |

| A3     | SDA        | Serial data input/output in the I <sup>2</sup> C Mode on LM3643.                                                                                  |

| B1     | SW         | Drain Connection for Internal NMOS and Synchronous PMOS Switches.                                                                                 |

| B2     | STROBE     | Active high hardware flash enable. Drive STROBE high to turn on Flash pulse. Internal pulldown resistor of 300 k $\Omega$ between STROBE and GND. |

| B3     | SCL        | Serial clock input for LM3643.                                                                                                                    |

| C1     | OUT        | Step-up DC/DC Converter Output. Connect a 10-µF ceramic capacitor between this terminal and GND.                                                  |

| C2     | HWEN       | Active high enable pin. High = Standby, Low = Shutdown/Reset. Internal pulldown resistor of 300 k $\Omega$ between HWEN and GND.                  |

| C3     | TORCH/TEMP | Torch terminal input or threshold detector for NTC temperature sensing and current scale back.                                                    |

| D1     | LED2       | High-side current source output for flash LED.                                                                                                    |

| D2     | ТХ         | Configurable dual polarity power amplifier synchronization input. Internal pulldown resistor of 300 $\mbox{k}\Omega$ between TX and GND.          |

| D3     | LED1       | High-side current source output for flash LED.                                                                                                    |

#### LM3643, LM3643A

SNVS967A - AUGUST 2014 - REVISED NOVEMBER 2014

TEXAS INSTRUMENTS

www.ti.com

### 8 Specifications

#### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                             | MIN      | MAX                                             | UNIT |

|---------------------------------------------|----------|-------------------------------------------------|------|

| IN, SW, OUT, LED1, LED2                     | -0.3     | 6                                               |      |

| SDA, SCL, TX, TORCH/TEMP, HWEN, STROBE      |          | -0.3 to the lesser of $(V_{IN}+0.3)$ w/ 6 V max |      |

| Continuous power dissipation <sup>(3)</sup> | Internal | y limited                                       |      |

| Junction temperature (T <sub>J-MAX</sub> )  |          | 150                                             |      |

| Maximum lead temperature (soldering)        | Not      | e <sup>(4)</sup>                                |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND terminal.

(3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typ.) and disengages at T<sub>J</sub> = 135°C (typ.). Thermal shutdown is ensured by design.

(4) For detailed soldering specifications and information, please refer to TI Application Note DSBGA Wafer Level Chip Scale Package (SNVA009).

#### 8.2 Handling Ratings

|                                            |                                                                                          |                                                                      | MIN   | MAX  | UNIT |

|--------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------|------|------|

| T <sub>stg</sub>                           | Storage temperature rang                                                                 | e                                                                    | -65   | 150  | °C   |

| V <sub>(ESD)</sub> Electrostatic discharge | Electrostatio discharge                                                                  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all $pins^{(1)}$ | -2500 | 2500 | V    |

|                                            | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | -1500                                                                | 1500  | V    |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                      | MIN | MAX | UNIT |

|------------------------------------------------------|-----|-----|------|

| V <sub>IN</sub>                                      | 2.5 | 5.5 | V    |

| Junction temperature (T <sub>J</sub> )               | -40 | 125 | *0   |

| Ambient temperature (T <sub>A</sub> ) <sup>(3)</sup> | -40 | 85  | -0   |

Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND terminal.

(3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (R<sub>θJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

#### 8.4 Thermal Information

|                                                         | LM3643  |      |

|---------------------------------------------------------|---------|------|

| THERMAL METRIC <sup>(1)</sup>                           | DSBGA   | UNIT |

|                                                         | 12 PINS |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance | 67.8    | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 8.5 Electrical Characteristics

Typical limits tested at  $T_A = 25^{\circ}$ C. Minimum and maximum limits apply over the full operating ambient temperature range (-40°C ≤  $T_A ≤ 85^{\circ}$ C). Unless otherwise specified,  $V_{IN} = 3.6$  V, HWEN =  $V_{IN}$ .<sup>(1)(2)</sup>

|                      | PARAMETER                                  | TEST CONDITI                                                                       | ONS                  | MIN  | ТҮР  | MAX             | UNIT  |

|----------------------|--------------------------------------------|------------------------------------------------------------------------------------|----------------------|------|------|-----------------|-------|

| CURREN               | T SOURCE SPECIFICATIONS                    |                                                                                    |                      |      |      |                 |       |

| 1                    | Current source accuracy                    | V <sub>OUT</sub> = 4 V, flash code = 0x7F = 1.5 A<br>flash                         |                      | -7%  | 1.5  | 7%              | А     |

| LED1/2               | Current source accuracy                    | $V_{OUT} = 4 V$ , torch code = 0 torch                                             | x3F = 89.3 mA        | -10% | 89.3 | 10%             | mA    |

| V <sub>HR</sub>      | LED1 and LED2 current source               | $I_{LED1/2} = 729 \text{ mA}$                                                      | Flash                |      | 290  |                 | mV    |

| VHR                  | regulation voltage                         | I <sub>LED1/2</sub> = 179 mA                                                       | Torch                |      | 158  |                 | IIIV  |

| V                    |                                            | ON threshold                                                                       |                      | 4.86 | 5    | 5.1             | V     |

| V <sub>OVP</sub>     |                                            | OFF threshold                                                                      |                      | 4.75 | 4.88 | 4.99            | v     |

| STEP-UP              | DC/DC CONVERTER SPECIFICATIO               | ONS                                                                                |                      |      |      |                 |       |

| R <sub>PMOS</sub>    | PMOS switch on-resistance                  |                                                                                    |                      |      | 86   |                 | mΩ    |

| R <sub>NMOS</sub>    | NMOS switch on-resistance                  |                                                                                    |                      |      | 65   |                 | 11122 |

|                      | Switch current limit                       | Reg 0x07, bit[0] = 0                                                               |                      | -12% | 1.9  | 12%             | •     |

| I <sub>CL</sub>      | Switch current limit                       | Reg 0x07, bit[0] = 1                                                               | Reg 0x07, bit[0] = 1 |      | 2.8  | 12%             | A     |

| UVLO                 | Undervoltage lockout threshold             | Falling V <sub>IN</sub>                                                            |                      | -2%  | 2.5  | 2%              | V     |

| V <sub>TRIP</sub>    | NTC comparator trip threshold              | Reg 0x09, bits[3:1] = '100'                                                        |                      | -5%  | 0.6  | 5%              | V     |

| I <sub>NTC</sub>     | NTC current                                |                                                                                    |                      | -6%  | 50   | 6%              | μA    |

| V <sub>IVFM</sub>    | Input voltage flash monitor trip threshold | Reg 0x02, bits[5:3] = '000'                                                        |                      | -3%  | 2.9  | 3%              | V     |

| l <sub>Q</sub>       | Quiescent supply current                   | Device not switching pass                                                          | mode                 |      | 0.3  | 0.75            | mA    |

| I <sub>SD</sub>      | Shutdown supply current                    | Device disabled, HWEN = $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ | 0 V                  |      | 0.1  | 4               | μA    |

| I <sub>SB</sub>      | Standby supply current                     | Device disabled, HWEN = $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ | 1.8 V                |      | 2.5  | 10              | μA    |

| HWEN, T              | ORCH/TEMP, STROBE, TX VOLTAG               | E SPECIFICATIONS                                                                   |                      |      |      |                 |       |

| VIL                  | Input logic low                            |                                                                                    |                      | 0    |      | 0.4             | V     |

| V <sub>IH</sub>      | Input logic high                           | $-2.5 V \le V_{IN} \le 5.5 V$                                                      |                      | 1.2  |      | V <sub>IN</sub> | v     |

| I <sup>2</sup> C-COM | PATIBLE INTERFACE SPECIFICATION            | ONS (SCL, SDA)                                                                     |                      |      |      |                 |       |

| V <sub>IL</sub>      | Input logic low                            | 25//////////                                                                       |                      | 0    |      | 0.4             | V     |

| V <sub>IH</sub>      | Input logic high                           | 2.5 V ≤ V <sub>IN</sub> ≤ 4.2 V                                                    |                      | 1.2  |      | V <sub>IN</sub> | v     |

| V <sub>OL</sub>      | Output logic low                           | I <sub>LOAD</sub> = 3 mA                                                           |                      |      |      | 400             | mV    |

(1) Minimum (Min) and Maximum (Max) limits are specified by design, test, or statistical analysis. Typical (typ.) numbers are not verified, but do represent the most likely norm. Unless otherwise specified, conditions for typical specifications are:  $V_{IN} = 3.6$  V and  $T_A = 25^{\circ}$ C.

(2) All voltages are with respect to the potential at the GND pin.

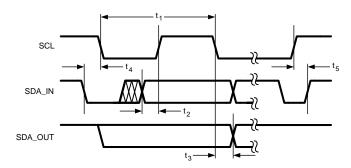

#### 8.6 Timing Requirements

|                |                                          | MIN | NOM | MAX | UNIT |

|----------------|------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub> | SCL clock period                         | 2.4 |     |     | μs   |

| t <sub>2</sub> | Data in set-up time to SCL high          | 100 |     |     |      |

| t <sub>3</sub> | Data out stable After SCL low            | 0   |     |     |      |

| t <sub>4</sub> | SDA low set-up time to SCL Low (start)   | 100 |     |     | ns   |

| t <sub>5</sub> | SDA high hold time after SCL high (stop) | 100 |     |     |      |

### 8.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|              | PARAMETER           | TEST CONDITIONS                                              | MIN | ТҮР | MAX | UNIT |

|--------------|---------------------|--------------------------------------------------------------|-----|-----|-----|------|

| $f_{\sf SW}$ | Switching frequency | $2.5 \text{ V} \leq \text{V}_{\text{IN}} \leq 5.5 \text{ V}$ | -6% | 4   | 6%  | MHz  |

Figure 1. I<sup>2</sup>C-Compatible Interface Specifications

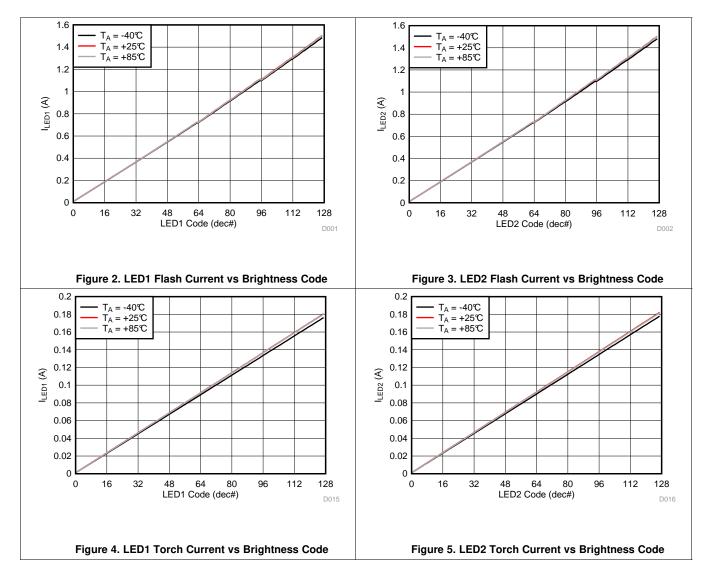

#### 8.8 Typical Characteristics

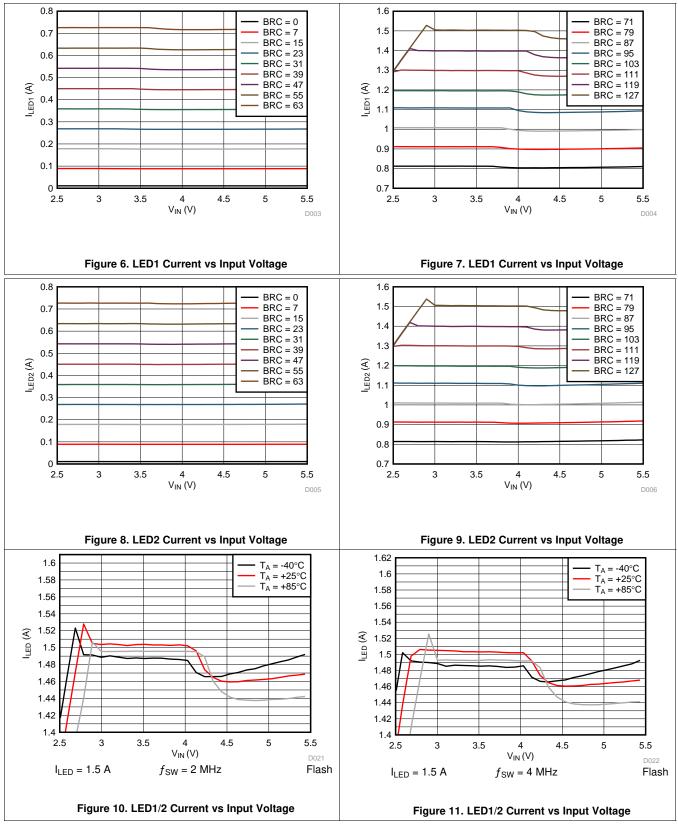

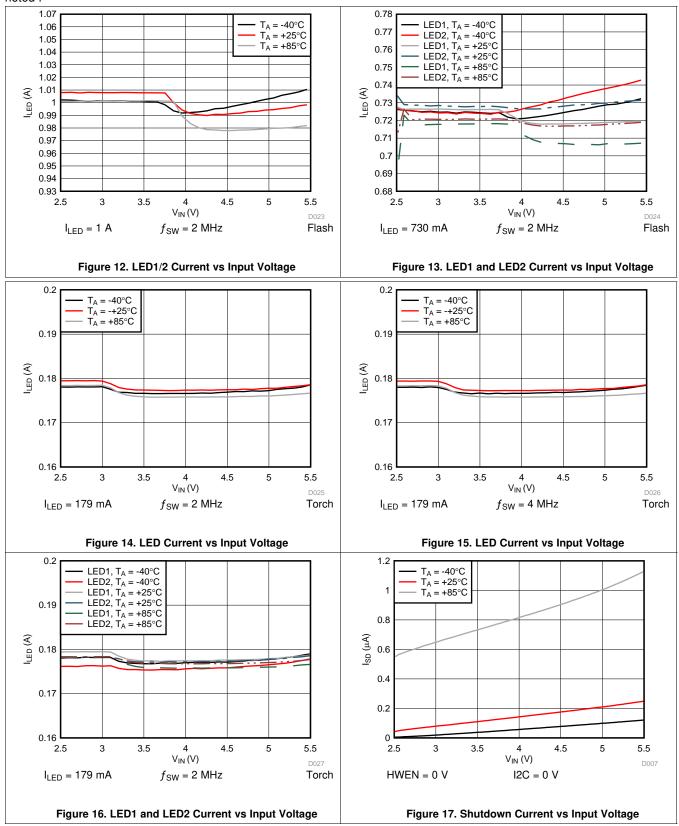

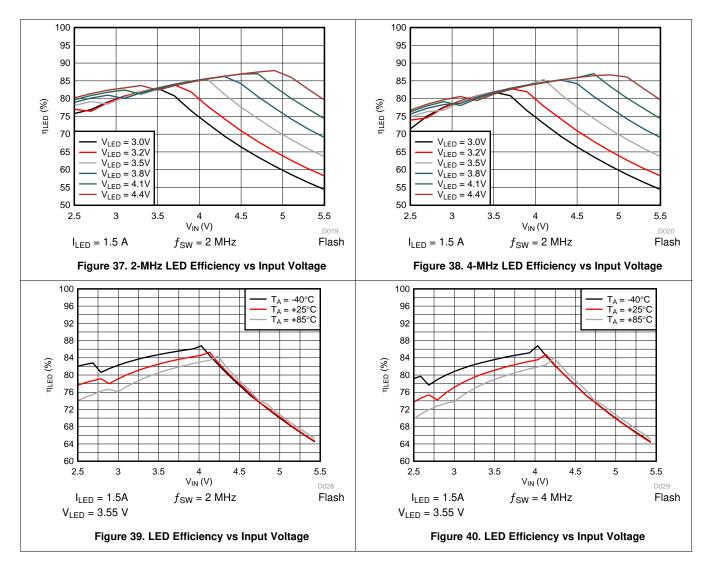

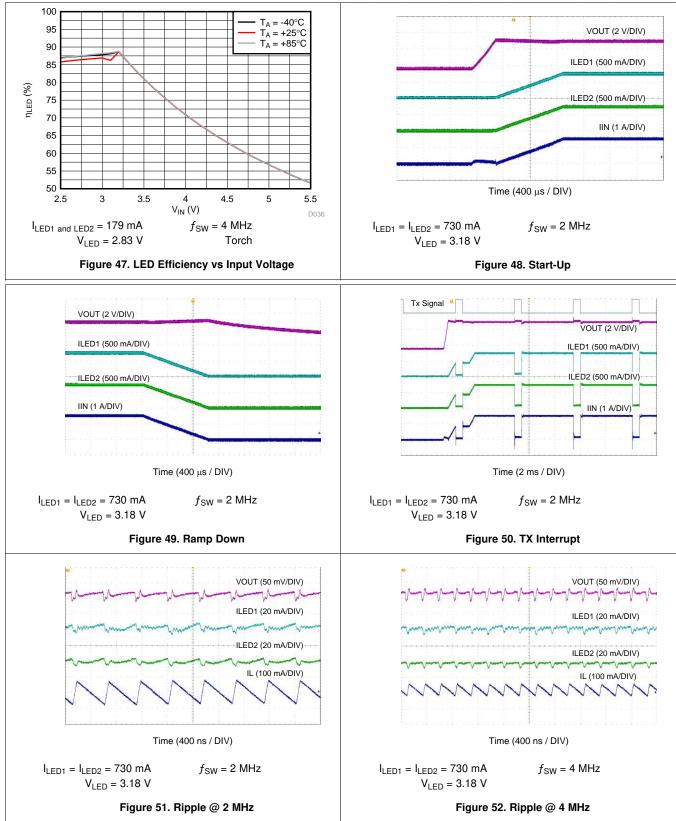

Ambient temperature is 25°C, input voltage is 3.6 V, HWEN =  $V_{IN}$ ,  $C_{IN} = C_{OUT} = 2 \times 10 \ \mu\text{F}$  and L = 1  $\mu\text{H}$ , unless otherwise noted .

#### **Typical Characteristics (continued)**

Ambient temperature is 25°C, input voltage is 3.6 V, HWEN =  $V_{IN}$ ,  $C_{IN} = C_{OUT} = 2 \times 10 \mu$ F and L = 1  $\mu$ H, unless otherwise noted .

Copyright © 2014, Texas Instruments Incorporated

Submit Documentation Feedback 7

#### LM3643, LM3643A

SNVS967A - AUGUST 2014 - REVISED NOVEMBER 2014

www.ti.com

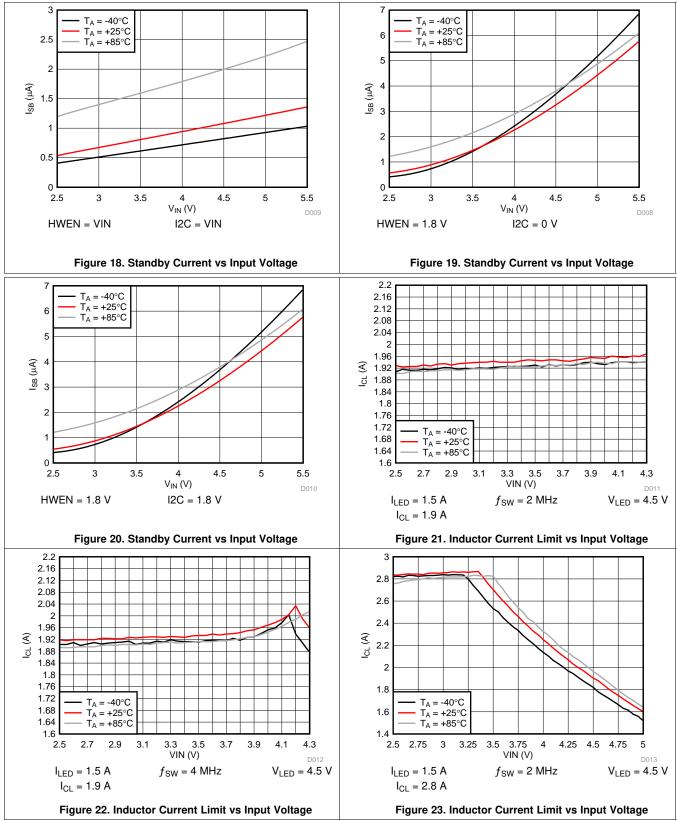

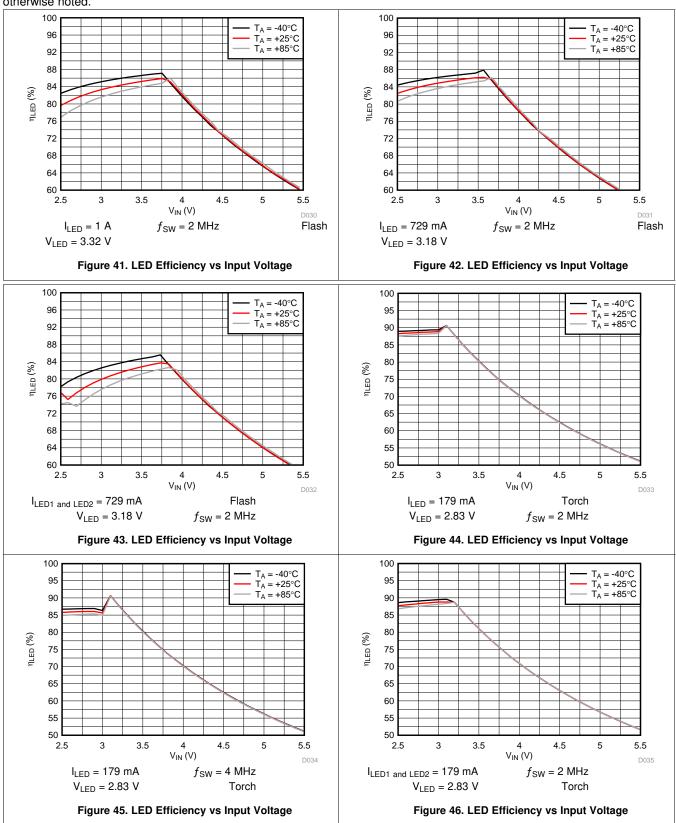

### **Typical Characteristics (continued)**

Ambient temperature is 25°C, input voltage is 3.6 V, HWEN =  $V_{IN}$ ,  $C_{IN} = C_{OUT} = 2 \times 10 \ \mu\text{F}$  and L = 1  $\mu\text{H}$ , unless otherwise noted .

8

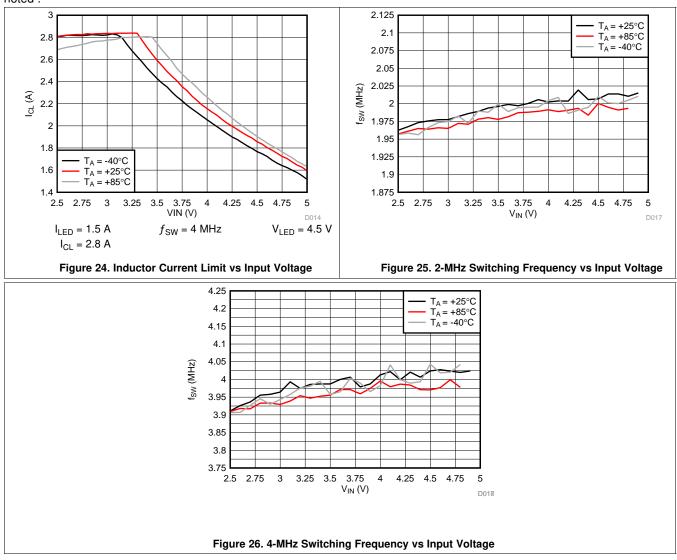

#### **Typical Characteristics (continued)**

Ambient temperature is 25°C, input voltage is 3.6 V, HWEN =  $V_{IN}$ ,  $C_{IN} = C_{OUT} = 2 \times 10 \ \mu\text{F}$  and L = 1  $\mu\text{H}$ , unless otherwise noted .

Copyright © 2014, Texas Instruments Incorporated

#### LM3643, LM3643A

SNVS967A - AUGUST 2014 - REVISED NOVEMBER 2014

**NSTRUMENTS**

**FEXAS**

#### **Typical Characteristics (continued)**

Ambient temperature is 25°C, input voltage is 3.6 V, HWEN =  $V_{IN}$ ,  $C_{IN} = C_{OUT} = 2 \times 10 \ \mu\text{F}$  and L = 1  $\mu\text{H}$ , unless otherwise noted .

## 9 Detailed Description

### 9.1 Overview

The LM3643 is a high-power white LED flash driver capable of delivering up to 1.5 A in either of the two parallel LEDs. The total allowed LED current during operation of the LM3643 ( $I_{LED1}+I_{LED2}$ ) is 1.5 A. The device incorporates a 2-MHz or 4-MHz constant frequency-synchronous current-mode PWM boost converter and dual high-side current sources to regulate the LED current over the 2.5-V to 5.5-V input voltage range.

The LM3643 PWM DC/DC boost converter switches and boosts the output to maintain at least V<sub>HR</sub> across each of the current sources (LED1/2). This minimum headroom voltage ensures that both current sources remain in regulation. If the input voltage is above the LED voltage + current source headroom voltage the device does not switch, but turns the PFET on continuously (Pass mode). In Pass mode the difference between (V<sub>IN</sub> - I<sub>LED</sub> x R<sub>PMOS</sub>) and the voltage across the LED is dropped across the current source.

#### **Overview (continued)**

The LM3643 has three logic inputs including a hardware Flash Enable (STROBE), a hardware Torch Enable (TORCH/TEMP, TORCH = default), and a Flash Interrupt input (TX) designed to interrupt the flash pulse during high battery-current conditions. These logic inputs have internal  $300-k\Omega$  (typ.) pulldown resistors to GND.

Additional features of the LM3643 include an internal comparator for LED thermal sensing via an external NTC thermistor and an input voltage monitor that can reduce the Flash current during low  $V_{IN}$  conditions. It also has a Hardware Enable (HWEN) pin that can be used to reset the state of the device and the registers by pulling the HWEN pin to ground.

Control is done via an  $I^2$ C-compatible interface. This includes adjustment of the Flash and Torch current levels, changing the Flash Timeout Duration, and changing the switch current limit. Additionally, there are flag and status bits that indicate flash current time-out, LED overtemperature condition, LED failure (open/short), device thermal shutdown, TX interrupt, and V<sub>IN</sub> undervoltage conditions.

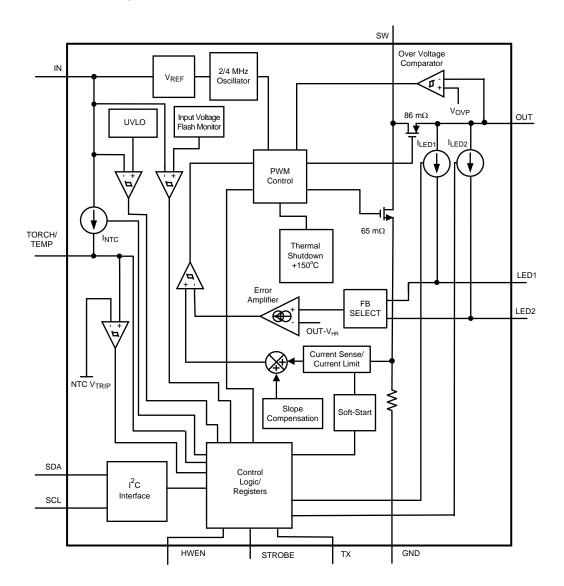

#### 9.2 Functional Block Diagram

#### 9.3 Feature Description

#### 9.3.1 Flash Mode

In Flash Mode, the LED current sources (LED1/2) provide 128 target current levels from 10.9 mA to 1500 mA. **The total allowed LED current during operation is 1.5A** ( $I_{LED1} + I_{LED2} = 1.5$  A). Once the Flash sequence is activated the current source (LED) ramps up to the programmed Flash current by stepping through all current steps until the programmed current is reached. The headroom in the two current sources can be regulated to provide 10.9 mA to 1.5 A on each of the two output legs. There is an option in the register settings to keep the two currents in the output leg the same.

When the device is enabled in Flash Mode through the Enable Register, all mode bits in the Enable Register are cleared after a flash time-out event.

#### 9.3.2 Torch Mode

In Torch mode, the LED current sources (LED1/2) provide 128 target current levels from 0.977 mA to 179 mA. The Torch currents are adjusted via the LED1 and LED2 LED Torch Brightness Registers. Torch mode is activated by the Enable Register (setting M1, M0 to '10'), or by pulling the TORCH/TEMP pin HIGH when the pin is enabled (Enable Register) and set to Torch Mode. Once the TORCH sequence is activated the active current sources (LED1/2) ramps up to the programmed Torch current by stepping through all current steps until the programmed current is reached. The rate at which the current ramps is determined by the value chosen in the Timing Register.

Torch Mode is not affected by Flash Timeout or by a TX Interrupt event.

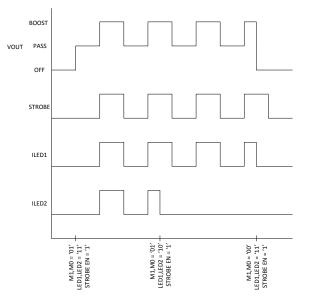

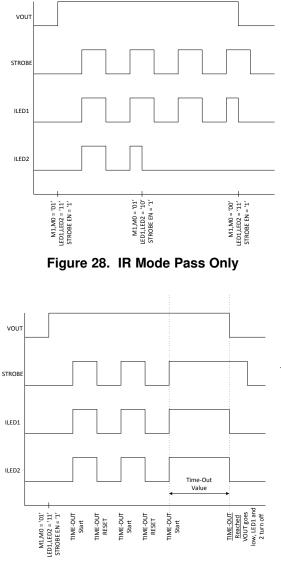

#### 9.3.3 IR Mode

In IR Mode, the target LED current is equal to the value stored in the LED1/2 Flash Brightness Registers. When IR mode is enabled (setting M1, M0 to '01'), the boost converter turns on and set the output equal to the input (pass-mode). At this point, toggling the STROBE pin enables and disables the LED1/2 current sources (if enabled). The strobe pin can only be set to be Level sensitive, meaning all timing of the IR pulse is externally controlled. In IR Mode, the current sources do not ramp the LED outputs to the target. The current transitions immediately from off to on and then on to off.

Figure 27. IR Mode with Boost

#### Feature Description (continued)

Figure 29. IR Mode Timeout

#### 9.4 Device Functioning Modes

#### 9.4.1 Start-Up (Enabling The Device)

Turn on of the LM3643 Torch and Flash modes can be done through the Enable Register. On start-up, when  $V_{OUT}$  is less than  $V_{IN}$  the internal synchronous PFET turns on as a current source and delivers 200 mA (typ.) to the output capacitor. During this time the current source (LED) is off. When the voltage across the output capacitor reaches 2.2 V (typ.) the current source turns on. At turnon the current source steps through each FLASH or TORCH level until the target LED current is reached. This gives the device a controlled turnon and limits inrush current from the V<sub>IN</sub> supply.

#### Copyright © 2014, Texas Instruments Incorporated

#### LM3643, LM3643A SNVS967A – AUGUST 2014 – REVISED NOVEMBER 2014

www.ti.com

#### **Device Functioning Modes (continued)**

#### 9.4.2 Pass Mode

The LM3643 starts up in Pass Mode and stays there until Boost Mode is needed to maintain regulation. If the voltage difference between  $V_{OUT}$  and  $V_{LED}$  falls below  $V_{HR}$ , the device switches to Boost Mode. In Pass Mode the boost converter does not switch, and the synchronous PFET turns fully on bringing  $V_{OUT}$  up to  $V_{IN} - I_{LED} \times R_{PMOS}$ . In Pass Mode the inductor current is not limited by the peak current limit.

#### 9.4.3 Power Amplifier Synchronization (TX)

The TX pin is a Power Amplifier Synchronization input. This is designed to reduce the flash LED current and thus limit the battery current during high battery current conditions such as PA transmit events. When the LM3643 is engaged in a Flash event, and the TX pin is pulled high, the LED current is forced into Torch Mode at the programmed Torch current setting. If the TX pin is then pulled low before the Flash pulse terminates, the LED current returns to the previous Flash current level. At the end of the Flash time-out, whether the TX pin is high or low, the LED current turns off.

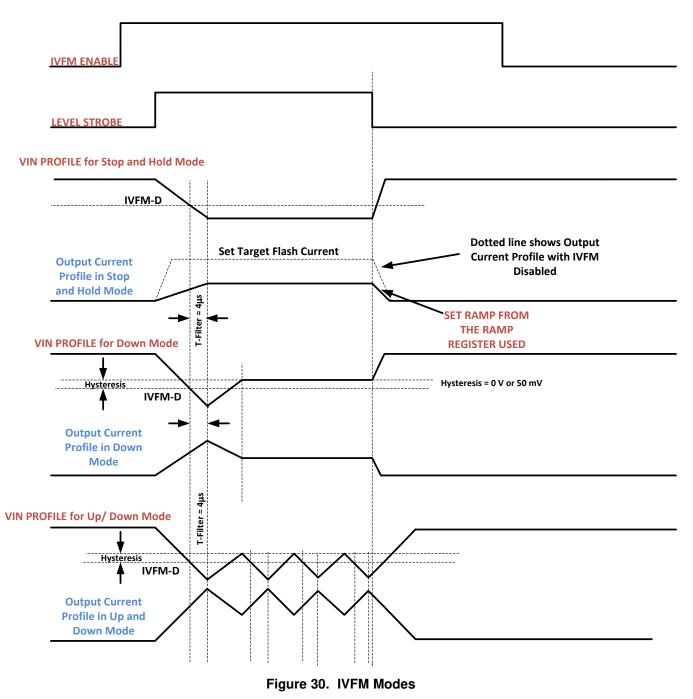

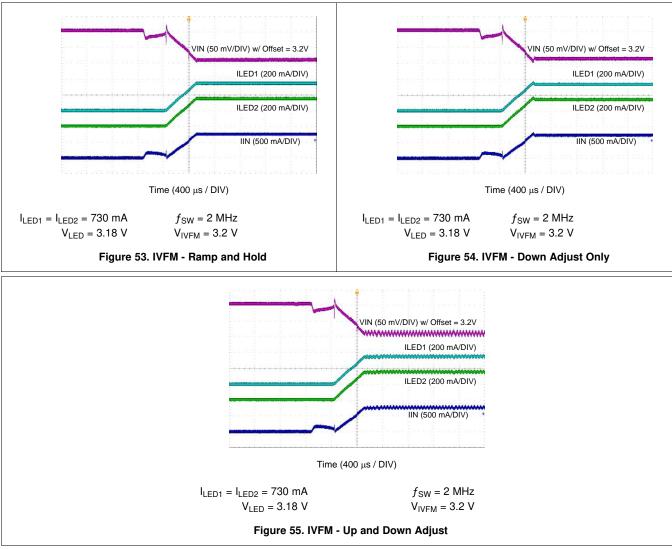

#### 9.4.4 Input Voltage Flash Monitor (IVFM)

The LM3643 has the ability to adjust the flash current based upon the voltage level present at the IN pin utilizing the Input Voltage Flash Monitor (IVFM). The adjustable threshold IVFM-D ranges from 2.9 V to 3.6 V in 100-mV steps, with three different usage modes (Stop and Hold, Adjust Down Only, Adjust Up and Down). The Flags2 Register has the IVFM flag bit set when the input voltage crosses the IVFM-D value. Additionally, the IVFM-D threshold sets the input voltage boundary that forces the LM3643 to either stop ramping the flash current during start-up (Stop and Hold Mode) or to start decreasing the LED current during the flash (Down Adjust Only and Up and Down Adjust). In Adjust Up and Down mode, the IVFM-D value plus the hysteresis voltage threshold set the input voltage boundary that forces the LM3643 to start ramping the flash current back up towards the target.

#### **Device Functioning Modes (continued)**

#### **Device Functioning Modes (continued)**

#### 9.4.5 Fault/Protections

#### 9.4.5.1 Fault Operation

If the LM3643 enters a fault condition, the device sets the appropriate flag in the Flags1 and Flags2 Registers (0x0A and 0x0B), and place the device into standby by clearing the Mode Bits ([1],[0]) in the Enable Register. The LM3643 remains in standby until an I<sup>2</sup>C read of the Flags1 and Flags2 Registers are completed. Upon clearing the flags/faults, the device can be restarted (Flash, Torch, IR, etc.). If the fault is still present, the LM3643 re-enters the fault state and enters standby again.

#### 9.4.5.2 Flash Time-Out

The Flash Time-Out period sets the amount of time that the Flash Current is being sourced from the current sources (LED1/2). The LM3643 has 16 timeout levels ranging from 10 ms to 400 ms (see *Timing Configuration Register (0x08)* for more detail).

#### 9.4.5.3 Overvoltage Protection (OVP)

The output voltage is limited to typically 5 V (see  $V_{OVP}$  spec in the *Electrical Characteristics*). In situations such as an open LED, the LM3643 raises the output voltage in order to try and keep the LED current at its target value. When  $V_{OUT}$  reaches 5 V (typ.) the overvoltage comparator trips and turns off the internal NFET. When  $V_{OUT}$  falls below the " $V_{OVP}$  Off Threshold", the LM3643 begins switching again. The mode bits are cleared, and the OVP flag is set, when an OVP condition is present for three rising OVP edges. This prevents momentary OVP events from forcing the device to shut down.

#### 9.4.5.4 Current Limit

The LM3643 features two selectable inductor current limits that are programmable through the I<sup>2</sup>C-compatible interface. When the inductor current limit is reached, the LM3643 terminates the charging phase of the switching cycle. Switching resumes at the start of the next switching period. If the overcurrent condition persists, the device operates continuously in current limit.

Since the current limit is sensed in the NMOS switch, there is no mechanism to limit the current when the device operates in Pass Mode (current does not flow through the NMOS in pass mode). In Boost mode or Pass mode if  $V_{OUT}$  falls below 2.3 V, the device stops switching, and the PFET operates as a current source limiting the current to 200 mA. This prevents damage to the LM3643 and excessive current draw from the battery during output short-circuit conditions. The mode bits are not cleared upon a Current Limit event, but a flag is set.

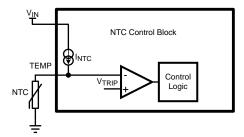

#### 9.4.5.5 NTC Thermistor Input (Torch/Temp)

The TORCH/TEMP pin, when set to TEMP mode, serves as a threshold detector and bias source for negative temperature coefficient (NTC) thermistors. When the voltage at TEMP goes below the programmed threshold, the LM3643 is placed into standby mode. The NTC threshold voltage is adjustable from 200 mV to 900 mV in 100-mV steps. The NTC bias current is set to 50  $\mu$ A. The NTC detection circuitry can be enabled or disabled via the Enable Register. If enabled, the NTC block turns on and off during the start and stop of a Flash/Torch event.

Additionally, the NTC input looks for an open NTC connection and a shorted NTC connection. If the NTC input falls below 100 mV, the NTC short flag is set, and the device is disabled. If the NTC input rises above 2.3 V, the NTC Open flag is set, and the device is disabled. These fault detections can be individually disabled/enabled via the NTC Open Fault Enable bit and the NTC Short Fault Enable bit.

Figure 31. Temp Detection Diagram

#### **Device Functioning Modes (continued)**

#### 9.4.5.6 Undervoltage Lockout (UVLO)

The LM3643 has an internal comparator that monitors the voltage at IN and forces the LM3643 into standby if the input voltage drops to 2.5 V. If the UVLO monitor threshold is tripped, the UVLO flag bit is set in the Flags1 Register (0x0A). If the input voltage rises above 2.5 V, the LM3643 is not available for operation until there is an I<sup>2</sup>C read of the Flags1 Register (0x0A). Upon a read, the Flags1 register is cleared, and normal operation can resume if the input voltage is greater than 2.5 V.

#### 9.4.5.7 Thermal Shutdown (TSD)

When the LM3643 die temperature reaches 150°C, the thermal shutdown detection circuit trips, forcing the LM3643 into standby and writing a '1' to the corresponding bit of the Flags1 Register (0x0A) (Thermal Shutdown bit). The LM3643 is only allowed to restart after the Flags1 Register (0x0A) is read, clearing the fault flag. Upon restart, if the die temperature is still above 150°C, the LM3643 resets the Fault flag and re-enters standby.

#### 9.4.5.8 LED and/or VOUT Short Fault

The LED Fault flags read back a '1' if the device is active in Flash or Torch mode and either active LED output experiences a short condition. The Output Short Fault flag reads back a '1' if the device is active in Flash or Torch mode and the boost output experiences a short condition. An LED short condition is determined if the voltage at LED1 or LED2 goes below 500 mV (typ.) while the device is in Torch or Flash mode. There is a deglitch time of 256  $\mu$ s before the LED Short flag is valid and a deglitch time of 2.048 ms before the VOUT Short flag is valid. The LED Short Faults can be reset to '0' by removing power to the LM3643, setting HWEN to '0', setting the SW RESET bit to a '1', or by reading back the Flags1 Register (0x0A on LM3643). The mode bits are cleared upon an LED and/or V<sub>OUT</sub> short fault.

#### 9.5 Programming

#### 9.5.1 Control Truth Table

| MODE1 | MODE0 | STROBE EN | TORCH EN | STROBE PIN | TORCH PIN | ACTION           |

|-------|-------|-----------|----------|------------|-----------|------------------|

| 0     | 0     | 0         | 0        | Х          | Х         | Standby          |

| 0     | 0     | 0         | 1        | Х          | pos edge  | Ext Torch        |

| 0     | 0     | 1         | 0        | pos edge   | Х         | Ext Flash        |

| 0     | 0     | 1         | 1        | 0          | pos edge  | Standalone Torch |

| 0     | 0     | 1         | 1        | pos edge   | 0         | Standalone Flash |

| 0     | 0     | 1         | 1        | pos edge   | pos edge  | Standalone Flash |

| 1     | 0     | Х         | Х        | Х          | Х         | Int Torch        |

| 1     | 1     | Х         | Х        | Х          | Х         | Int Flash        |

| 0     | 1     | 0         | Х        | Х          | Х         | IRLED Standby    |

| 0     | 1     | 1         | Х        | 0          | Х         | IRLED Standby    |

| 0     | 1     | 1         | Х        | pos edge   | Х         | IRLED enabled    |

#### 9.5.2 I<sup>2</sup>C-Compatible Interface

#### 9.5.2.1 Data Validity

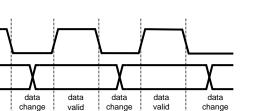

The data on SDA must be stable during the HIGH period of the clock signal (SCL). In other words, the state of the data line can only be changed when SCL is LOW.

SCL

SDA

allowed ' allowed ' allowed

Figure 32. Data Validity Data

A pullup resistor between the controller's VIO line and SDA must be greater than  $[(VIO-V_{OL}) / 3mA]$  to meet the  $V_{OL}$  requirement on SDA. Using a larger pullup resistor results in lower switching current with slower edges, while using a smaller pullup results in higher switching currents with faster edges.

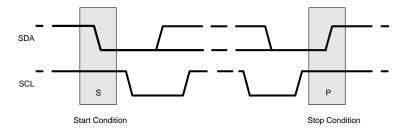

#### 9.5.2.2 Start and Stop Conditions

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as the SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 33. Start and Stop Conditions

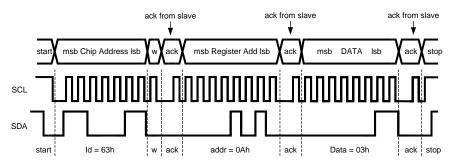

#### 9.5.2.3 Transferring Data

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The LM3643 pulls down the SDA line during the 9th clock pulse, signifying an acknowledge. The LM3643 generates an acknowledge after each byte is received. There is no acknowledge created after data is read from the device.

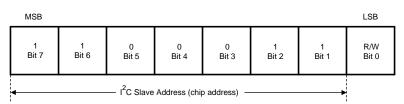

After the START condition, the  $I^2C$  master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3643 7-bit address is 0x63. The device address for the LM3643A is 0x67. For the eighth bit, a '0' indicates a WRITE and a '1' indicates a READ. The second byte selects the register to which the data is written. The third byte contains data to write to the selected register.

Figure 34. Write Cycle W = Write (SDA = "0") R = Read (SDA = "1") Ack = Acknowledge (SDA Pulled Down by Either Master or Slave) ID = Chip Address, 63h for LM3643

#### 9.5.2.4 PC-Compatible Chip Address

The device address for the LM3643 is 1100011 (0x63). The device address for the LM3643A is 1100111 (0x67). After the START condition, the I<sup>2</sup>C-compatible master sends the 7-bit address followed by an eighth read or write bit (R/W). R/W = 0 indicates a WRITE and R/W = 1 indicates a READ. The second byte following the device address selects the register address to which the data is written. The third byte contains the data for the selected register.

Figure 35. I<sup>2</sup>C-Compatible Chip Address

#### 9.6 Register Descriptions

|                                |                      | POWER ON/RESET VALUE |

|--------------------------------|----------------------|----------------------|

| REGISTER NAME                  | INTERNAL HEX ADDRESS | LM3643               |

| Enable Register                | 0x01                 | 0x80                 |

| IVFM Register                  | 0x02                 | 0x01                 |

| LED1 Flash Brightness Register | 0×03                 | 0xBF                 |

| LED2 Flash Brightness Register | 0x04                 | 0x3F                 |

| LED1 Torch Brightness Register | 0×05                 | 0xBF                 |

| LED2 Torch Brightness Register | 0×06                 | 0x3F                 |

| Boost Configuration Register   | 0x07                 | 0x09                 |

| Timing Configuration Register  | 0×08                 | 0x1A                 |

| TEMP Register                  | 0×09                 | 0x08                 |

| Flags1 Register                | 0x0A                 | 0x00                 |

| Flags2 Register                | 0x0B                 | 0x00                 |

| Device ID Register             | 0x0C                 | 0x02                 |

| Last Flash Register            | 0x0D                 | 0x00                 |

#### 9.6.1 Enable Register (0x01)

| Bit 7                                                             | Bit 6                                                                       | Bit 5                                                      | Bit 4                                                                               | Bit 3                                                                                            | Bit 2 | Bit 1                                          | Bit 0                                         |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|------------------------------------------------|-----------------------------------------------|

| <b>TX Pin Enable</b><br>0 = Disabled<br>1 = Enabled<br>(Default ) | Strobe Type<br>0 = Level<br>Triggered<br>(Default)<br>1 = Edge<br>Triggered | Strobe Enable<br>0 = Disabled<br>(Default )<br>1 = Enabled | <b>TORCH/TEMP</b><br><b>Pin Enable</b><br>0 = Disabled<br>(Default )<br>1 = Enabled | <b>Mode Bits: M1, M</b><br>'00' = Standby (Di<br>'01' = IR Drive<br>'10' = Torch<br>'11' = Flash |       | LED2 Enable<br>0 = OFF<br>(Default )<br>1 = ON | LED1 Enable<br>0 = OFF<br>(Default)<br>1 = ON |

#### NOTE

Edge Strobe Mode is not valid in IR MODE. Switching between Level and Edge Strobe Types while the device is enabled is not recommended.

In Edge or Level Strobe Mode, it is recommended that the trigger pulse width be set greater than 1 ms to ensure proper turn-on of the device.

#### LM3643, LM3643A

SNVS967A - AUGUST 2014 - REVISED NOVEMBER 2014

www.ti.com

#### 9.6.2 IVFM Register (0x02)

| Bit 7 | Bit 6                                                                      | Bit 5                                                                                                                                 | Bit 4  | Bit 3 | Bit 2                                                    | Bit 1                                                                                    | Bit 0 |

|-------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------------------------------------------------------|------------------------------------------------------------------------------------------|-------|

| RFU   | UVLO<br>Circuitry<br>(Default)<br>0 = Disabled<br>(Default)<br>1 = Enabled | IVFM Levels<br>000 = 2.9 V (De<br>001 = 3 V<br>010 = 3.1 V<br>011 = 3.2 V<br>100 = 3.3 V<br>101 = 3.4 V<br>110 = 3.5 V<br>111 = 3.6 V | fault) |       | IVFM<br>Hysteresis<br>0 = 0 mV<br>(Default)<br>1 = 50 mV | IVFM Selection<br>00 = Disabled<br>01 = Stop and Ho<br>10 = Down Mode<br>11 = Up and Dow |       |

#### NOTE

IVFM Mode Bits are static once the LM3643 is enabled in Torch, Flash or IR modes. If the IVFM mode needs to be updated, disable the device and then change the mode bits to the desired state.

#### 9.6.3 LED1 Flash Brightness Register (0x03)

| Bit 7                                                                                                                                                                                 | Bit 6                                                                                                        | Bit 5                                  | Bit 4            | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|-----------|-------|-------|-------|

| LED2 Flash<br>Current<br>Override<br>0 = LED2<br>Flash Current<br>is not set to<br>LED1 Flash<br>Current<br>1 = LED2<br>Flash Current<br>is set to LED1<br>Flash Current<br>(Default) | LED1 Flash Bri<br>I <sub>FLASH1/2</sub> (mA) ≈<br>0000000 = 10.9<br><br>0111111 = 729<br><br>1111111 = 1.5 A | (Brightness Code<br>mA<br>mA (Default) | ə × 11.725 mA) + | . 10.9 mA |       |       |       |

#### 9.6.4 LED2 Flash Brightness Register (0x04)

| Bit 7 | Bit 6                                                                                                               | Bit 5              | Bit 4            | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|-------|---------------------------------------------------------------------------------------------------------------------|--------------------|------------------|-----------|-------|-------|-------|

| RFU   | LED2 Flash Bri<br>I <sub>FLASH1/2</sub> (mA) ≈<br>0000000 = 10.9<br><br>0111111 = 729<br><br>1111111 = 1.5 <i>F</i> | mA<br>mA (Default) | ə × 11.725 mA) + | - 10.9 mA |       |       |       |

#### 9.6.5 LED1 Torch Brightness Register (0x05)

| Bit 7                                                                                                                                                                                 | Bit 6 | Bit 5        | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|--------|-------|-------|-------|

| LED2 Torch<br>Current<br>Override<br>0 = LED2<br>Torch Current<br>is not set to<br>LED1 Torch<br>Current<br>1 = LED2<br>Torch Current<br>is set to LED1<br>Torch Current<br>(Default) |       | mA (Default) |       | 977 mA |       |       |       |

LM3643, LM3643A

SNVS967A-AUGUST 2014-REVISED NOVEMBER 2014

#### 9.6.6 LED2 Torch Brightness Register (0x06)

| Bit 7 | Bit 6 | Bit 5        | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|--------------|-------|--------|-------|-------|-------|

| RFU   |       | mA (Default) |       | 977 mA |       |       |       |

#### 9.6.7 Boost Configuration Register (0x07)

| Bit 7                                                            | Bit 6 | Bit 5 | Bit 4 | Bit 3                                                                     | Bit 2                                                          | Bit 1                                                               | Bit 0                                                                 |

|------------------------------------------------------------------|-------|-------|-------|---------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|

| Software<br>Reset Bit<br>0 = Not Reset<br>(Default)<br>1 = Reset | RFU   | RFU   | RFU   | LED Pin Short<br>Fault Detect<br>0 = Disabled<br>1 = Enabled<br>(Default) | Boost Mode<br>0 = Normal<br>(Default)<br>1 = Pass Mode<br>Only | Boost<br>Frequency<br>Select<br>0 = 2 MHz<br>(Default)<br>1 = 4 MHz | Boost Current<br>Limit Setting<br>0 = 1.9 A<br>1 = 2.8 A<br>(Default) |

#### 9.6.8 Timing Configuration Register (0x08)

| Bit 6                            | Bit 5                                                                                                                                    | Bit 4                                                                                                                                          | Bit 3                                                                                                                                                             | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Torch Current I<br>000 = No Ramp | Ramp Time                                                                                                                                | Bit 4                                                                                                                                          | Flash Time-Out D<br>0000 = 10 ms<br>0001 = 20 ms<br>0010 = 30 ms<br>0011 = 40 ms<br>0101 = 60 ms<br>0110 = 70 ms<br>0111 = 80 ms<br>1000 = 90 ms<br>1001 = 100 ms | uration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                  |                                                                                                                                          |                                                                                                                                                |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                  | <b>Torch Current</b> I<br>000 = No Ramp<br>001 = 1 ms (Def<br>010 = 32 ms<br>011 = 64 ms<br>100 = 128 ms<br>101 = 256 ms<br>110 = 512 ms | Torch Current Ramp Time<br>000 = No Ramp<br>001 = 1 ms (Default)<br>010 = 32 ms<br>011 = 64 ms<br>100 = 128 ms<br>101 = 256 ms<br>110 = 512 ms | Torch Current Ramp Time<br>000 = No Ramp<br>001 = 1 ms (Default)<br>010 = 32 ms<br>011 = 64 ms<br>100 = 128 ms<br>101 = 256 ms<br>110 = 512 ms                    | Torch Current Ramp Time      Flash Time-Out D        000 = No Ramp      0000 = 10 ms        001 = 1 ms (Default)      0001 = 20 ms        010 = 32 ms      0010 = 30 ms        011 = 64 ms      0010 = 50 ms        100 = 128 ms      0100 = 50 ms        101 = 256 ms      0101 = 60 ms        111 = 1024 ms      0111 = 80 ms        100 = 90 ms      1001 = 150 ms (Default)        101 = 250 ms      1100 = 250 ms        101 = 250 ms      1101 = 300 ms        110 = 350 ms      110 = 350 ms | Torch Current Ramp Time      Flash Time-Out Duration        000 = No Ramp      0000 = 10 ms        001 = 1 ms (Default)      0001 = 20 ms        010 = 32 ms      0010 = 30 ms        011 = 64 ms      0011 = 40 ms        100 = 128 ms      0100 = 50 ms        101 = 256 ms      0101 = 60 ms        111 = 512 ms      0110 = 70 ms        111 = 1024 ms      0111 = 80 ms        1001 = 100 ms      1001 = 100 ms        1001 = 150 ms      1010 = 150 ms        101 = 250 ms      1100 = 250 ms        101 = 300 ms      1101 = 300 ms        111 = 300 ms      111 = 300 ms | Torch Current Ramp TimeFlash Time-Out Duration $000 = No Ramp$ $0000 = 10 ms$ $001 = 1 ms (Default)$ $0001 = 20 ms$ $010 = 32 ms$ $0010 = 30 ms$ $011 = 64 ms$ $0011 = 40 ms$ $100 = 128 ms$ $0100 = 50 ms$ $101 = 256 ms$ $0110 = 60 ms$ $110 = 512 ms$ $0110 = 70 ms$ $111 = 1024 ms$ $0111 = 80 ms$ $100 = 100 ms$ $1001 = 100 ms$ $100 = 250 ms$ $110 = 250 ms$ $110 = 250 ms$ $110 = 300 ms$ $110 = 300 ms$ $111 = 300 ms$ |  |  |

#### 9.6.9 TEMP Register (0x09)

| Bit 7 | Bit 6                                                                                                                                          | Bit 5                                                              | Bit 4                                                               | Bit 3                                                                                                                                           | Bit 2 | Bit 1 | Bit 0                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------------------------------------------------------------------------|

| RFU   | TORCH<br>Polarity<br>0 = Active<br>High (Default)<br>(Pulldown<br>Resistor<br>Enabled)<br>1 = Active Low<br>(Pulldown<br>Resistor<br>Disabled) | NTC Open<br>Fault Enable<br>0 = Disabled<br>(Default)<br>1 =Enable | NTC Short<br>Fault Enable<br>0 = Disabled<br>(Default)<br>1 =Enable | TEMP Detect Volt<br>000 = 0.2 V<br>001 = 0.3 V<br>010 = 0.4 V<br>011 = 0.5 V<br>100 = 0.6 V (Defau<br>101 = 0.7 V<br>110 = 0.8 V<br>111 = 0.9 V |       |       | TORCH/TEMP<br>Function<br>Select<br>0 = TORCH<br>(Default)<br>1 = TEMP |

#### NOTE

The Torch Polarity bit is static once the LM3643 is enabled in Torch, Flash or IR modes. If the Torch Polarity bit needs to be updated, disable the device and then change the Torch Polarity bit to the desired state.

#### LM3643, LM3643A

SNVS967A - AUGUST 2014 - REVISED NOVEMBER 2014

NSTRUMENTS

Texas

### 9.6.10 Flags1 Register (0x0A)

| Bit 7   | Bit 6                           | Bit 5                | Bit 4                | Bit 3                 | Bit 2                              | Bit 1      | Bit 0                  |

|---------|---------------------------------|----------------------|----------------------|-----------------------|------------------------------------|------------|------------------------|

| TX Flag | V <sub>OUT</sub> Short<br>Fault | VLED1 Short<br>Fault | VLED2 Short<br>Fault | Current Limit<br>Flag | Thermal<br>Shutdown<br>(TSD) Fault | UVLO Fault | Flash Time-Out<br>Flag |

### 9.6.11 Flags2 Register (0x0B)

| Bit 7 | Bit 6 | Bit 5 | Bit 4              | Bit 3          | Bit 2             | Bit 1     | Bit 0              |

|-------|-------|-------|--------------------|----------------|-------------------|-----------|--------------------|

| RFU   | RFU   | RFU   | NTC Short<br>Fault | NTC Open Fault | IVFM Trip<br>Flag | OVP Fault | TEMP Trip<br>Fault |

#### 9.6.12 Device ID Register (0x0C)

| Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2           | Bit 1 | Bit 0 |

|-------|-------|-----------|-------|-------|-----------------|-------|-------|

| RFU   | RFU   | Device ID |       |       | Silicon Revisio | n Bit |       |

|       |       | '000'     |       |       | '010'           |       |       |

### 9.6.13 Last Flash Register (0x0D)

| Bit 7 | Bit 6            | Bit 5              | Bit 4               | Bit 3                | Bit 2                                       | Bit 1              | Bit 0          |

|-------|------------------|--------------------|---------------------|----------------------|---------------------------------------------|--------------------|----------------|

| RFU   | The value stored | d is always the la | st current value th | ne IVFM detection bl | lock set. I <sub>LED</sub> = I <sub>F</sub> | LASH-TARGET × ((CO | de + 1) / 128) |

#### 10 Applications and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **10.1** Application Information

The LM3643 can drive two flash LEDs at currents up to 1.5 A per LED. The total LED current the LM3643 boost can deliver is 1.5 A ( $I_{LED1} + I_{LED2}$ ). The 2-MHz/4-MHz DC/DC boost regulator allows for the use of small value discrete external components.

#### **10.2 Typical Application**

Figure 36. LM3643 Typical Application

#### 10.2.1 Design Requirements

Example requirements based on default register values:

| DESIGN PARAMETER          | EXAMPLE VALUE             |

|---------------------------|---------------------------|

| Input Voltage Range       | 2.5 V to 5.5 V            |

| Brightness Control        | I <sup>2</sup> C Register |

| LED Configuration         | 2 Parallel Flash LEDs     |

| Boost Switching Frequency | 2 MHz (4 MHz selectable)  |

| Flash Brightness          | 750 mA per LED            |

10.2.2 Detailed Design Procedure

#### 10.2.2.1 Output Capacitor Selection

The LM3643 is designed to operate with a  $10-\mu$ F ceramic output capacitor. When the boost converter is running, the output capacitor supplies the load current during the boost converter on-time. When the NMOS switch turns off, the inductor energy is discharged through the internal PMOS switch, supplying power to the load and restoring charge to the output capacitor. This causes a sag in the output voltage during the on-time and a rise in the output voltage during the off-time. The output capacitor is therefore chosen to limit the output ripple to an acceptable level depending on load current and input/output voltage differentials and also to ensure the converter remains stable.

Larger capacitors such as a 22- $\mu$ F or capacitors in parallel can be used if lower output voltage ripple is desired. To estimate the output voltage ripple considering the ripple due to capacitor discharge ( $\Delta V_Q$ ) and the ripple due to the capacitors ESR ( $\Delta V_{ESR}$ ) use the following equations:

For continuous conduction mode, the output voltage ripple due to the capacitor discharge is:

$$\Delta V_{Q} = \frac{I_{LED} \times (V_{OUT} - V_{IN})}{f_{SW} \times V_{OUT} \times C_{OUT}}$$

The output voltage ripple due to the output capacitors ESR is found by:

$$\Delta V_{\text{ESR}} = R_{\text{ESR}} \times \left( \frac{I_{\text{LED}} \times V_{\text{OUT}}}{V_{\text{IN}}} + \Delta I_{\text{L}} \right)$$

where

$$\Delta I_{\text{I}} = \frac{V_{\text{IN}} \times (V_{\text{OUT}} - V_{\text{IN}})}{2 \pi (V_{\text{OUT}} - V_{\text{IN}})}$$

$\Delta I_{L} = \frac{1}{2 x f_{SW} x L x V_{OUT}}$

In ceramic capacitors the ESR is very low so the assumption is that 80% of the output voltage ripple is due to capacitor discharge and 20% from ESR. Table 1 lists different manufacturers for various output capacitors and their case sizes suitable for use with the LM3643.

#### 10.2.2.2 Input Capacitor Selection

Choosing the correct size and type of input capacitor helps minimize the voltage ripple caused by the switching of the LM3643 boost converter and reduce noise on the boost converter's input pin that can feed through and disrupt internal analog signals. In the typical application circuit a  $10-\mu$ F ceramic input capacitor works well. It is important to place the input capacitor as close as possible to the LM3643 input (IN) pin. This reduces the series resistance and inductance that can inject noise into the device due to the input switching currents. Table 1 lists various input capacitors recommended for use with the LM3643.

| MANUFACTURER    | PART NUMBER       | VALUE | CASE SIZE                         | VOLTAGE RATING |

|-----------------|-------------------|-------|-----------------------------------|----------------|

| TDK Corporation | C1608JB0J106M     | 10 µF | 0603 (1.6 mm × 0.8 mm × 0.8 mm)   | 6.3 V          |

| TDK Corporation | C2012JB1A106M     | 10 µF | 0805 (2.0 mm × 1.25 mm × 1.25 mm) | 10 V           |

| Murata          | GRM188R60J106M    | 10 µF | 0603 (1.6 mm x 0.8 mm x 0.8 mm)   | 6.3 V          |

| Murata          | GRM21BR61A106KE19 | 10 µF | 0805 (2.0 mm × 1.25 mm × 1.25 mm) | 10 V           |

Table 1. Recommended Input/Output Capacitors (X5R/X7R Dielectric)

#### 10.2.2.3 Inductor Selection

The LM3643 is designed to use a 0.47- $\mu$ H or 1- $\mu$ H inductor. Table 2 lists various inductors and their manufacturers that work well with the LM3643. When the device is boosting (V<sub>OUT</sub> > V<sub>IN</sub>) the inductor is typically the largest area of efficiency loss in the circuit. Therefore, choosing an inductor with the lowest possible series resistance is important. Additionally, the saturation rating of the inductor should be greater than the maximum operating peak current of the LM3643. This prevents excess efficiency loss that can occur with inductors that operate in saturation. For proper inductor operation and circuit performance, ensure that the inductor saturation and the peak current limit setting of the LM3643 are greater than I<sub>PEAK</sub> in the following calculation:

NSTRUMENTS

**EXAS**

(2)

$$I_{PEAK} = \frac{I_{LOAD}}{\eta} x \frac{V_{OUT}}{V_{IN}} + \Delta I_{L} \text{ where } \Delta I_{L} = \frac{V_{IN} x (V_{OUT} - V_{IN})}{2 x f_{SW} x L x V_{OUT}}$$

where

Efficiency details can be found in the Application Curves .

Table 2. Recommended Inductors

| MANUFACTURER | L       | PART NUMBER      | DIMENSIONS (L×W×H)       | I <sub>SAT</sub> | R <sub>DC</sub> |

|--------------|---------|------------------|--------------------------|------------------|-----------------|

| ТОКО         | 0.47 μH | DFE201610P-R470M | 2.0 mm x 1.6 mm x 1.0 mm | 4.1 A            | 32 mΩ           |

| ТОКО         | 1 µH    | DFE201610P-1R0M  | 2.0 mm x 1.6 mm x 1.0 mm | 3.7 A            | 58 mΩ           |

#### 10.2.3 Application Curves

Ambient temperature is 25°C, input voltage is 3.6V, HWEN =  $V_{IN}$ ,  $C_{IN} = 2 \times 10 \ \mu\text{F}$ ,  $C_{OUT} = 2 \times 10 \ \mu\text{F}$  and L = 1  $\mu\text{H}$ , unless otherwise noted.

(3)

LM3643, LM3643A SNVS967A – AUGUST 2014 – REVISED NOVEMBER 2014 **ISTRUMENTS**

**EXAS**

Ambient temperature is 25°C, input voltage is 3.6V, HWEN =  $V_{IN}$ ,  $C_{IN} = 2 \times 10 \ \mu\text{F}$ ,  $C_{OUT} = 2 \times 10 \ \mu\text{F}$  and L = 1  $\mu\text{H}$ , unless otherwise noted.

Ambient temperature is 25°C, input voltage is 3.6V, HWEN =  $V_{IN}$ ,  $C_{IN} = 2 \times 10 \mu$ F,  $C_{OUT} = 2 \times 10 \mu$ F and L = 1  $\mu$ H, unless otherwise noted.

LM3643, LM3643A SNVS967A – AUGUST 2014 – REVISED NOVEMBER 2014

www.ti.com

Ambient temperature is 25°C, input voltage is 3.6V, HWEN =  $V_{IN}$ ,  $C_{IN} = 2 \times 10 \ \mu\text{F}$ ,  $C_{OUT} = 2 \times 10 \ \mu\text{F}$  and L = 1  $\mu\text{H}$ , unless otherwise noted.

#### **11** Power Supply Recommendations

The LM3643 is designed to operate from an input voltage supply range between 2.5 V and 5.5 V. This input supply must be well regulated and capable to supply the required input current. If the input supply is located far from the LM3643 additional bulk capacitance may be required in addition to the ceramic bypass capacitors.

### 12 Layout

#### 12.1 Layout Guidelines

The high switching frequency and large switching currents of the LM3643 make the choice of layout important. The following steps should be used as a reference to ensure the device is stable and maintains proper LED current regulation across its intended operating voltage and current range.

- 1. Place  $C_{IN}$  on the top layer (same layer as the LM3643) and as close to the device as possible. The input capacitor conducts the driver currents during the low-side MOSFET turn-on and turn-off and can detect current spikes over 1 A in amplitude. Connecting the input capacitor through short, wide traces to both the IN and GND pins reduces the inductive voltage spikes that occur during switching which can corrupt the  $V_{IN}$  line.

- 2. Place  $C_{OUT}$  on the top layer (same layer as theLM3643) and as close as possible to the OUT and GND pin. The returns for both  $C_{IN}$  and  $C_{OUT}$  should come together at one point, as close to the GND pin as possible. Connecting  $C_{OUT}$  through short, wide traces reduce the series inductance on the OUT and GND pins that can corrupt the  $V_{OUT}$  and GND lines and cause excessive noise in the device and surrounding circuitry.

- 3. Connect the inductor on the top layer close to the SW pin. There should be a low-impedance connection from the inductor to SW due to the large DC inductor current, and at the same time the area occupied by the SW node should be small so as to reduce the capacitive coupling of the high dV/dT present at SW that can couple into nearby traces.

- 4. Avoid routing logic traces near the SW node so as to avoid any capacitively coupled voltages from SW onto any high-impedance logic lines such as TORCH/TEMP, STROBE, HWEN, SDA, and SCL. A good approach is to insert an inner layer GND plane underneath the SW node and between any nearby routed traces. This creates a shield from the electric field generated at SW.

- 5. Terminate the Flash LED cathodes directly to the GND pin of the LM3643. If possible, route the LED returns with a dedicated path so as to keep the high amplitude LED currents out of the GND plane. For Flash LEDs that are routed relatively far away from the LM3643, a good approach is to sandwich the forward and return current paths over the top of each other on two layers. This helps reduce the inductance of the LED current paths.

TEXAS INSTRUMENTS

www.ti.com

### 12.2 Layout Example

Figure 56. Layout Example

#### 13 Device and Documentation Support

#### 13.1 Device Support

#### 13.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 13.2 Related Documentation

#### 13.2.1 Related Links

Table 3 below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

| PARTS   | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL<br>DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|---------|----------------|--------------|------------------------|---------------------|---------------------|

| LM3643  | Click here     | Click here   | Click here             | Click here          | Click here          |

| LM3643A | Click here     | Click here   | Click here             | Click here          | Click here          |

#### Table 3. Related Links

#### 13.3 Trademarks

#### 13.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 13.5 Glossary

18 A

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

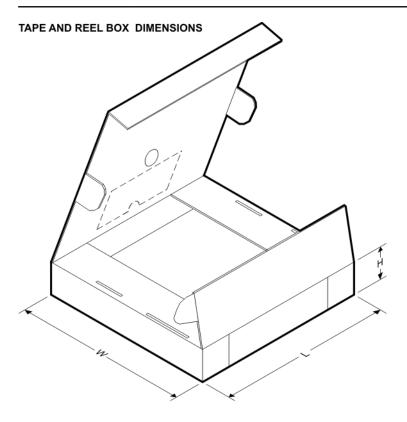

#### 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

10-Dec-2020

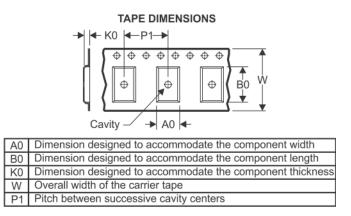

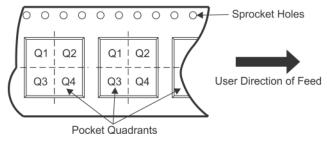

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LM3643AYFFR      | ACTIVE        | DSBGA        | YFF                | 12   | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 85    | ZAAI                    | Samples |

| LM3643YFFR       | ACTIVE        | DSBGA        | YFF                | 12   | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 85    | 3643                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.